# Dfx Design for Excellence (DFX)

Driving Product Optimization Through Early Stage Supplier Engagement

Brian Morrison, B.A.Sc., P. Eng. Director, Value Engineering & Technology Sept 21, 2015

manufacturing partner to innovators

# **SMTC** Corporation

- Established in 1985

- Over 600,000 square feet of manufacturing capability

- Facilities that covers a large global footprint

- More than 40 manufacturing and assembly lines

- Approximately 1,300 employees

- Listed on NASDAQ since 2000 (SMTX)

- Frost & Sullivan Awards Winners Growth Leadership and Product Quality Leadership Awards

### **Our Vision**

To simplify the lives of our customers by delivering extraordinary Customer Service, Responsiveness, Quality, Technology Solutions and Value, fueling their Success and Our growth

### **Our Values**

- Solution Oriented

- Proactive

- Collaborative Partner

- Innovative

- Professional integrity

- Dependable

## **Medical Device Markets**

# Specialists in the Design and Manufacture of Complex Class I and II Medical Devices

We design and manufacture class I and II medical devices that require a mix of highly specialized technologies including:

- Diagnostic devices

- Imaging equipment

- laboratory equipment

- Patient Monitoring systems

- Infusion Pumps

- Dispensing Systems

- Consumer Wellness Products.

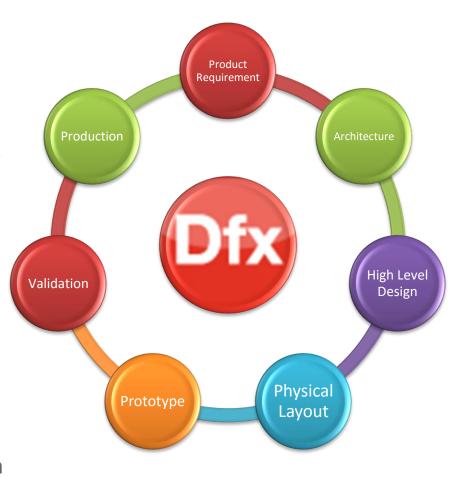

# **DFX Product Optimization**

- What is DFX?

- DFX Benefits

- Product Value Equation

- Ability to Impact Product Value

- Early Supplier Involvement (ESI)

- Product Development

- dFMEA

- Design for Reliability (DFR)

- Design for Supply Chain (DFSC)

- High Level Design

- Design for Testability (DFT)

- Physical Design

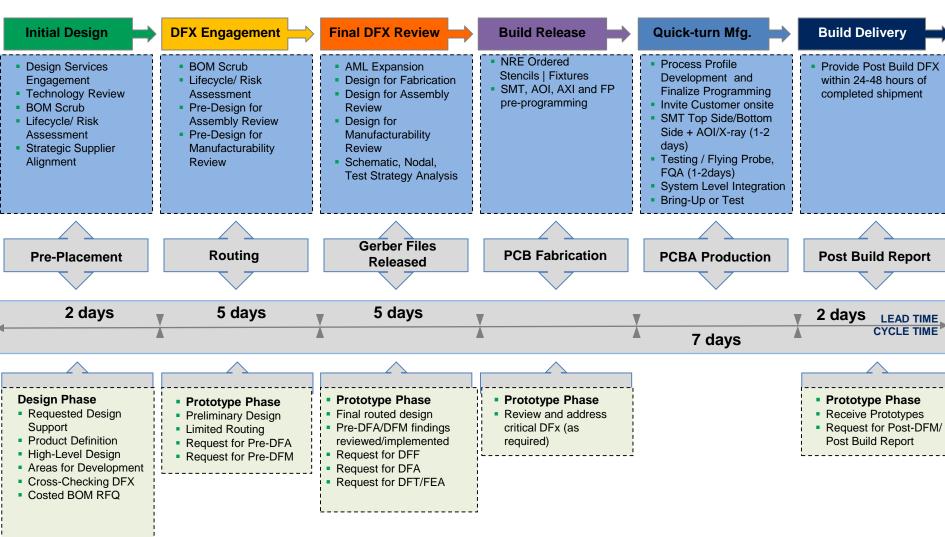

- PCB Design Engagement

- Design for Assembly (DFA)

- Design for Reliability (DFR)

- Design for Fabrication (DFF)

- Design for Testability (DFT)

- Prototype

- Design for Manufacturing (DFM)

- Validation

- Design for Reliability (DFR)

- New Product Introduction

- FMEA and Control Plan

- Production

- ESI Benefits

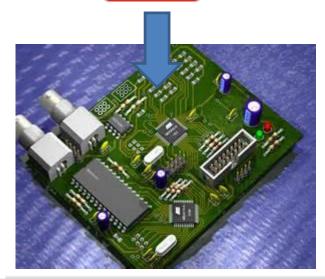

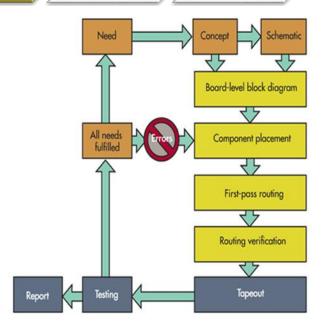

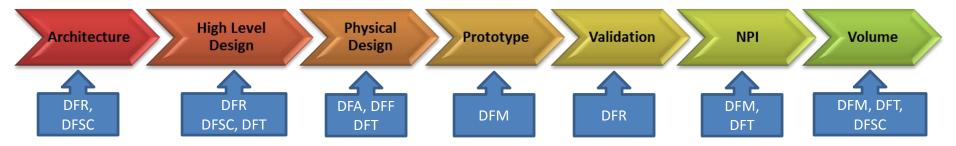

- DFX or Design for eXcellence is the application of Rules, Guidelines and Methodologies during the Product Development with the purpose of impacting it's Value while meeting the Product Design Requirements.

- The x in Dfx represents an aspect of the product value to be targeted; these may include (but not limited to)

- Design for Supply Chain (DFSC)

- Process of ensuring material sourcing, supply, compliancy and lifecycle requirements are met during design stage.

- Design for Reliability (DFR)

- Process for ensuring reliability of a product or system during the design stage before physical prototype

- Design for Fabrication (DFF)

- Process of ensuring the manufacturability of the PCB fabrication design and related cost drivers are met.

- Design for Assembly (DFA)

- Process of ensuring the assembly of the PCB design and physical layout rules are met prior to prototype

- Design for Manufacturability (DFM)

- Process of ensuring the manufacturability of a component or complete assembly to met supplier's capability.

- Design for Test (DFT)

- Process of analyzing test access, coverage and schematics are designed for test

## Product Design for Manufacturability

- Improved PCB yield, performance and cost (DFF)

- Improved Assembly yield and reduced labour content (DFA)

## Product Design for Testability

- Improved Coverage, Reliability and Final yield, reduced RMA and field failures. (DFT, DFR)

- Reduced development engineering resource commitment, improved time to market

## Product/ Process Stability and Repeatability

- Reduced lead time, improved availability/lifecycle and material costs (DFSC)

- High quality, reliable and robust performance for the life of the product (DFR)

## Capability

Improved Production Stability and Predictability (DFM)

## First Pass Yield and Capacity

Continuous Improvement (DFM)

# Product Value Equation

# **PERFORMANCE**

Performance can be a function, need, feature or aspect that is deemed critical to the product design.

Cost can include material, labor, test, logistics or any other aspect required to provide the required performance.

to innovators

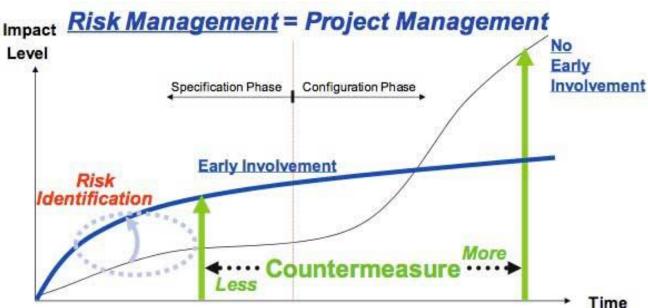

# Ability to Impact Product Value

# Early Supplier Involvement (ESI)

## **Common Development Mistakes**

- Lack of Collaboration and Review of Requirements

- Poor understanding of supplier capabilities/ limitations

- Customer expectations (reliability, lifetime, use environment) are not incorporated into the new product development

### **Best Practice**

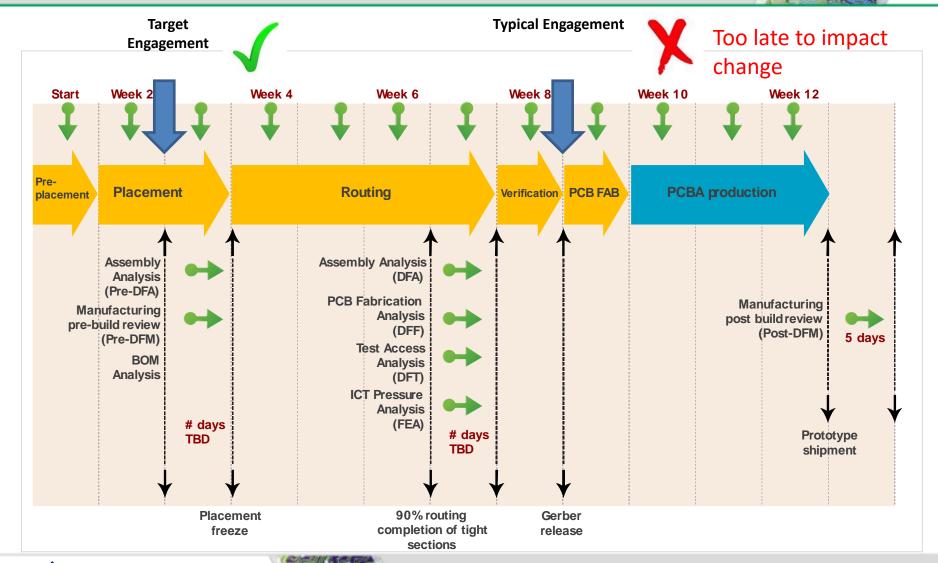

- Early supplier involvement in the product design cycle can provide customers with a product that is more cost effective, increased manufacturability and quality, has higher reliability and longer overall lifecycle.

- Design reviews at key stages throughout the design cycle provides critical feedback to address potential issues to ensure a successful new product introduction and high quality, high yielding, reliable and manufacturable product.

High Level Design

Physical Design

**Prototype**

**Validation**

NPI

Volume

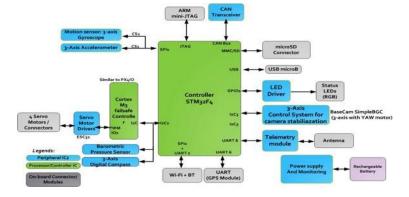

## **Architecture/ Concept Key Activities**

- Selection of Critical Components

- Defining Environment Requirements

- Detailed Specifications

- Hardware/ Software Requirements

- Defining Key Functions/ Features

## Supplier Engagement

- Major Component Suppliers

- Manufacturer

- Supply Chain/ Procurement

## **DFX Review**

- Design for Reliability (DFR)

- Critical Component Selection

- Desired Lifetime/ Environment

- PCB Design Considerations

- Design for Supply Chain (DFSC)

- Predicted Lifecycle and Sourcing

- Process Compatibility

- Strategic Supplier Alignment

## dFMEA - Design Failure Modes and Effects Analysis

High Level Design

Physical Design

Prototype

**Validation**

NPI

Volume

## **Impact of Design Decisions**

- Although very early in the design cycle, key component suppliers should be providing their component level dFMEA, reliability and design suitability input.

- Reliability and Lifetime decisions made now will be very difficult to change later in the design cycle. A through design review should be made.

- Sourcing and strategic alignment of the supply chain and a predicted EOL should be reviewed.

- Specifying a custom single sourced processor slated to go EOL can limit component availability, time to market and potentially require a complete redesign.

| Item | Part                                | Failure Mode             | Local Effect                                                                                                                                | System Effect                                                            | Module Name    | Cause | ICT (Y/N) | Mfg Controls                   | Comments |

|------|-------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|-------|-----------|--------------------------------|----------|

| 1.   | MSP430<br>(Link<br>Processor)<br>U1 | Pin 4 tied to<br>Pin 5   | No Effect assuming both are<br>configured as inputs<br>(internal pull up disabled)                                                          | 1: None                                                                  |                | N/A   | Y         | 5DX, AOI and<br>ICT Functional |          |

| 2.   | 01                                  | Pin 5 tied to<br>Pin 6   | No Effect assuming both<br>pins are inputs                                                                                                  | 1: None                                                                  |                | N/A   | Y         | 5DX, AOI and<br>ICT Functional |          |

| 3.   |                                     | Pin 6 tied to<br>Pin 7   | No Effect assuming both<br>pins are inputs                                                                                                  | 1: None                                                                  |                | N/A   | Y         | 5DX, AOI and<br>ICT Functional |          |

| 4.   |                                     | Pin 7 tied to<br>Pin 8   | No Effect assuming both<br>pins are inputs                                                                                                  | 1: None                                                                  |                | N/A   | Y         | 5DX, AOI and<br>ICT Functional |          |

| 5.   |                                     | Pin 8 tied to<br>Pin 9   | Unintended additional load<br>of 0.25mA on internal<br>reference supply of<br>MSP430. (internal pull up<br>disabled on pin 8)<br>No effect. | 1: None                                                                  |                | N/A   | Y         | 5DX, AOI and<br>ICT Functional |          |

| 6.   |                                     | Pin 9 tied to<br>Pin 10  | ADC internal reference<br>circuit will get damaged in<br>MSP430. Analog voltage<br>monitoring cannot be done<br>by MSP430                   | 115:<br>Communication<br>Module power<br>faults will not be<br>monitored |                | N/A   | Y         | 5DX, AOI and<br>ICT Functional |          |

| 7.   |                                     | Pin 10 tied to<br>Pin 11 | Short circuit protection<br>feature will be triggered in<br>U3.<br>MSP430 will not get Analog<br>power supply.                              | 115:<br>Communication<br>Module power<br>faults will not be<br>monitored |                | N/A   | Y         | 5DX, AOI and<br>ICT Functional |          |

| 8.   |                                     | Pin 11 tied to<br>Pin 12 | Short circuit protection<br>feature will be triggered in<br>U3.<br>MSP430 will not get Analog<br>power supply.                              | 115:<br>Communication<br>Module power<br>faults will not be<br>monitored | Link Processor | N/A   | Y         | 5DX, AOI and<br>ICT Functional |          |

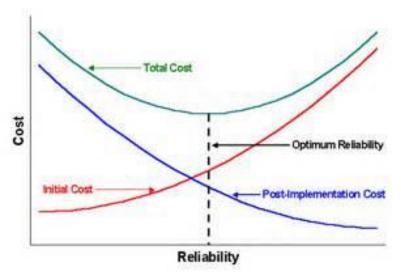

# Design for Reliability (DFR)

DFR is performed early in the design cycle to identify approved manufacturer part numbers which for reasons lifecycle, availability, process compatibility or validity are addressed prior to initial design

### Critical Component Considerations

- Sensitivity of the circuit to component performance

- Number of components within the circuit

- Output from FMEA (Failure Mode Effects Analysis)

- Historical experience/ Industry data

- Component technology

- Tin Whiskers

- Ceramic Capacitor (Cyclic Voltage)

- Resistors (High Resistance SIR)

- Thick Film Resistors (Sulfide Corrosion)

- Electrolytic Capacitors

- Connectors

- Wear Out Memory, Relay/Switches/ LED

### Desired Lifetime

Temperature/ Humidity/ Electrical Load/ Vibration/ Mechanical Stress/ Shock/ Power Cycling

### PCB Design

- Surface Finish OSP, ENIG, HASL, Immersion Silver

- Stack up, Laminate (Tg/Td), Blind/Buried Vias, Microfill/ Plating

- Land Pattern Design, Spacing, Voltage Bias

- ICT Stress

# Design for Supply Chain (DFSC)

DFSC performed early in the design cycle helps to identify selected manufacturer part numbers which for reasons of lifecycle, availability, process compatibility or validity are addressed prior to initial design.

### BOM Health Check

- Review AML data for completeness (orderable) and preferred supply.

- Ensure MPN match with part description

- Hazardous Substance Content

- Manufacturing Process Compatibility

### BOM Lifecycle Analysis

- Form-Fit-Function (FFF) replacement reviews

- Predicted Lifecycle and YTEOL Forecasts

- Change Notices and Counterfeit Alerts

### Value Add

- AML Expansion and Preferred supplier selection

- Supply Chain Optimization

- EOL and Alternate Qualification

- Cost Reduction

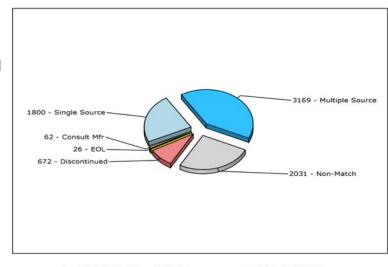

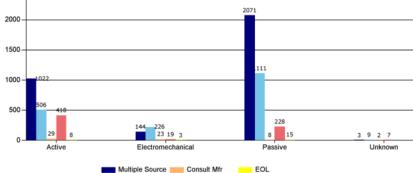

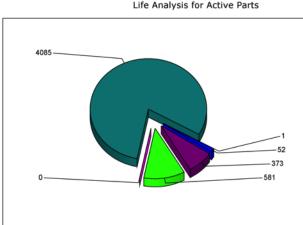

## **BOM Health Check**

- A BOM Health Analysis services can be performed utilizing leading providers of component information on the global market and economy.

- Advanced reporting tools and prediction services can provide insight on Risk and make informed decisions prior to securing the architecture.

### Health Analysis

- Provides an overall health of the BOM supply chain based on current and predicted lifecycle, available sources and compliancy.

- AML

| • | Total AML:        | 7883 |

|---|-------------------|------|

| • | Total Active AML: | 5093 |

Risk:

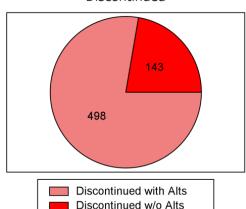

| • | Discontinued w/o Alts:  | 142  |

|---|-------------------------|------|

| • | Discontinued with Alts: | 498  |

| • | EOL:                    | 26   |

| • | Single Sourced          | 1860 |

| • | RoHS Non-Compliant      | 87   |

- Calculated Health Score:

- 612.6 out of a possible 1000

### **Health Analysis**

2500

Single Source Discontinued

BOM Analysis provides insight to identifying opportunities and focus to improve supply chain health and AML alternates to address single sourced, EOL/Discontinued, Non-compliant and address material cost drivers.

### Risk Areas

Discontinued AML: 498 w/ alt, 143 w/o alt.

EOL AML: 26

Non-compliant: 86

Single Sourced AML - 1800

### Value Add

- Evaluate FFF replacement recommendations or develop strategy to address Discontinued/EOL components.

- Qualify RoHS equivalent orderable part numbers or provide alternates to address compliancy issues

- Align strategic FFF AML Alternates to provide multiple sources to single sourced components.

- Identify opportunities for cost reduction through FFF AML Alternate on existing AML.

- Provide PCN support to proactively notify and address risk

Discontinued

AML Expansion Project A

### **Scope of the Project**

Targeting cost reduction, 40 parts were identified as FFF alternates to existing approved AML with a potential for 20% reduction in material costs.

Cost avoidance of \$38K was identified through alternate sourcing due to obsolesce

### **Value Engineering Services Implemented**

**Cost Savings**

Component Engineering

• \$126K

AML Expansion Project B

### **Scope of the Project**

Target cost reduction and in-plant store VMI for Power Supply for a potential 8% reduction in cost. Full functional part evaluation in system and test reports provided to support qualification

### **Value Engineering Services Implemented**

**Cost Savings**

Component Engineering

• \$87K

High Level Design

Physical Design

**Prototype**

**Validation**

NPI

Volume

## Hardware Design

- Schematic Design

- ASIC/ FBGA Design

- Cont'd Component Selection

- Hardware/ Software Requirements

- Defining Key Functions/ Features

- Test and Performance Definition

## Who should be engaged?

- Supply Chain/ Procurement

- Software Engineers

- Test Development Partners

- Manufacturer

## **DfX Review**

- Design for Testability

- Schematic Review

- Test Strategy Review

- Design for Supply Chain (DFSC)

- Predicted Lifecycle and Sourcing

- Process Compatibility

- Strategic Supplier Alignment

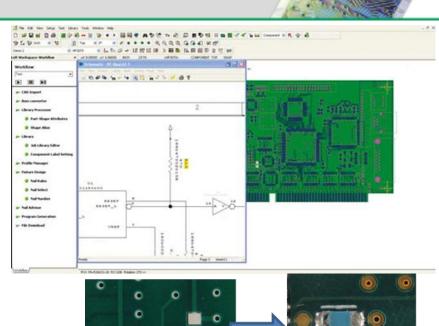

# Design for Testability (DFT)

- Early electrical design can be reviewed at the schematic level to identify electrical characteristics of the design that may have a negative impact on in-circuit test coverage or cost.

- Design rule and guidelines checks applied through advanced schematic modelling software can identify costly design errors at high level design.

- Advanced reporting provide comprehensive reports that highlight estimated production yield, test coverage by component, cycle times and validate early dFMEA assumptions.

- Adjustments to the schematic at this high level design to address access and design considerations including JTAG, Boundary Scan and related requirements can significantly reduce the overall cost and complexity of the test strategy.

**Architecture**

High Level Design Physical Design

Prototype

**Validation**

NPI

Volume

## PCB Design

- PCB Layout and Routing

- PCB Stackup and Fabrication

- Final Component Selection

- Passives

- Hardware

- Design File Generation (Gerber, Fab, Placement)

## Who should be engaged?

- PCB Designers

- Manufacturers

- PCB Fabrication

- Test Development Partners

## **DfX Review**

- Design for Assembly (DFA)

- Physical Layout

- Assembly and Manufacturer

- Design for Fabrication (DFF)

- Stack up and Impedance

- PCB Fabrication Design Rules

- Design for Testability (DFT)

- Nodal Analysis

- Test Strategy Development

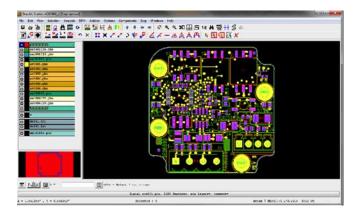

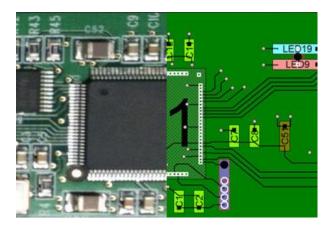

# PCB Design Engagement

# Design for Assembly (DFA)

- Design for Assembly targets opportunities in the physical layout of the assembly to identify areas for improvement and potential areas of concern to drive assembly cost out early in the design cycle.

- Rules and Guidelines are based on your manufacturers capabilities and component requirements.

- Design rules must be configured for your product requirements. i.e. Class 2 or 3, Reliability (Safety critical)

- Advanced software and combined with years of assembly experience. 500+ DFA checks can be performed to provide results on;

- Component Analysis

- Pad stack Analysis

- Pin to Pad Analysis

- Test Point Analysis

- Solder Paste Analysis

# Dfx Design for Assembly (DFA)

Example DFA Output outlining Critical (Major), Hot (Yield improvement), Warm (Minor), Cool (No immediate concern) and Ignore (acceptable)

# Design for Reliability (DFR)

- Design for Assembly Reports are an important tool to provide insight into Product failures

- Utilizing Six Sigma, estimated annualized cost avoidances can be assign to prioritize design change decisions.

- Analysis can be performed to address issues early in the design address potential reliability issues.

Ref Des U37, U38, distance between pad too close (0.0059"). Prone to solder bridge. Recommend decreasing pad from 13.78 mil to 11 mils.

Ref R1050, C239, RN96, FB2, etc., masked trace between toe print is too thin, may break and cause insufficient solder. Minimum recommended clearance between exposed via and toeprint is 5mil.

Ref Des U48, U103, land pattern is not optimal, heel distance is too big. Too much heel may cause solder bridge under component, not visible to visual inspection. Recommended to decrease by 25 mil on heel side.

### **Quality and Reliability Concern.**

2 OFE, 130 Locations – 260 Opportunities Probability of Occurrence 50% Expected Yield Detractor 2.5% Rework Cost \$2.80

Potential Failure Cost \$4,021.01

### **Quality and Reliability Concern.**

28 OFE, 14 Location – 392 Opportunities Probability of Occurrence 40% Expected Yield Detractor 0.72% Rework Cost \$0.42

Potential Failure Cost \$727.50

### **Quality and Reliability Concern.**

50 OFE, 2 Location – 100 Opportunities Probability of Occurrence 50% Expected Yield Detractor 0.23% Rework Cost \$0.70

**Potential Failure Cost \$386.63**

# Design for Fabrication (DFF)

- DFF is intended to help review customers' designs with respect to PCB manufacturability as early in the design cycle as possible, where it is easy to make decisions that drive out cost, improve fabrication yields and address concerns before final design is completed.

- Reviews typically include determining workable stackups, including impedance trace widths.

- Most supplier utilize automated DFX tools such as Valor to apply their internal Design Rule Checks (DRC) and will provide comprehensive DFM reports for Design Reviews.

Description

Taiyo 4000-BN

1/2oz Sig (Std Pit)

370H

2oz P/G

370H

1oz Sig

370H

2oz P/G

370H

2oz P/G

370H

# Design for Fabrication (DFF)

Suppliers will typically provide their DFM guidelines upon request.

| VIAS                                     |                         | <u>.                                    </u> |                                         | -t B.0::::               | 0040054700                                 |                                       | _ |          | -     |

|------------------------------------------|-------------------------|----------------------------------------------|-----------------------------------------|--------------------------|--------------------------------------------|---------------------------------------|---|----------|-------|

| Customer:                                |                         |                                              |                                         |                          | 20130517903                                | i0                                    |   |          |       |

| Part#:                                   | ABC                     |                                              |                                         | Account Mgr.:            | D D-1                                      |                                       |   |          |       |

| Revision:                                | In a Donal              |                                              |                                         |                          | Reza Bahram                                | I                                     |   |          |       |

| Cust contact:                            | Joe Byna                |                                              |                                         | Date                     | 5/31/2013                                  |                                       |   |          |       |

| Category                                 | Cust. Data              | Edited<br>Manufacturing<br>Data              | Predicted<br>Finished<br>Values         | Production<br>Preference | Production<br>Minimum<br>(Based on<br>Hoz) | Eng.<br>Approval<br>Required          | Ô | Verified |       |

| Min. Line Width:                         |                         |                                              |                                         |                          |                                            |                                       |   |          |       |

| External Layers                          | 0.0035                  |                                              |                                         | 0.004                    | 0.0035                                     | <0.0035                               |   | ☑        |       |

| Internal Layers                          | 0.0035                  |                                              |                                         | 0.004                    | 0.0035                                     | <0.0035                               |   | ☑        |       |

| idths less<br>nan .006 wide to minimi:   | ao antunnio otoki       | during the ciluar immer                      | cion process                            |                          |                                            |                                       |   | 1        |       |

|                                          |                         | oards, the minin                             |                                         | 0. si pacina is          | 045 (Hoz coppe                             | r)                                    |   | 1        |       |

| Min. Spacing:                            |                         |                                              |                                         |                          |                                            | X                                     |   |          |       |

| External Layers                          | 0.0034                  |                                              |                                         | 0.004                    | 0.0035                                     | <0.0035                               |   | ☑        |       |

| Internal Layers                          | 0.0034                  |                                              |                                         | 0.004                    | 0.00325                                    | < 0.00325                             |   | ☑        |       |

|                                          |                         |                                              |                                         |                          |                                            |                                       |   |          |       |

| uter copper wt:                          | 0.50                    | (Prior to plating                            | • ///////////////////////////////////// |                          | V Yes                                      | ///////////////////////////////////// |   | V        |       |

| outer spacing ade<br>iner copper wt:     | quate to suppo<br>0.5/1 | ort specified coppe                          | r weight?                               |                          | M 162                                      | □ INO                                 |   | <b>9</b> |       |

| inner spacing ade                        | 0.0.1                   | t appoified coppe                            | r woight?                               |                          | V Yes                                      | <i>∏</i> No                           |   | <u> </u> |       |

| inner spacing ade                        | quate to suppo          | ort specified coppe                          | r weight?                               |                          |                                            | XIIIIIIII                             |   |          |       |

| Min.Embedded<br>Trace-To-Gnd<br>Spacing: |                         |                                              |                                         |                          |                                            |                                       |   |          |       |

| External Layers                          | 0.0148                  |                                              |                                         | 0.005                    | **0.005                                    | <0.005                                |   | ☑        |       |

| Internal Layers                          | 0.0148                  |                                              |                                         | 0.005                    | 0.005                                      | <0.005                                |   | ☑        |       |

|                                          | ly boards, th           | e minimum emb                                | edded feati                             | ures spacing i           | s .006 (after et                           | ch comp).                             |   |          |       |

| lin. Hole To Cu.<br>Spacing:             |                         |                                              |                                         |                          |                                            |                                       |   |          |       |

| Internal Layers                          | <0.005                  |                                              |                                         | 0.010                    | 0.008                                      | <0.008                                |   | <b>v</b> | seend |

| Min. Annular<br>Ring:                    |                         |                                              |                                         |                          |                                            |                                       |   |          |       |

| External Lavers                          | 0.004                   |                                              |                                         | 0.005                    | 0.005                                      | <0.005                                |   | Ø        |       |

Incorporating these rules into your native

Design Package can help drive value

further up the Product Development

Cycle

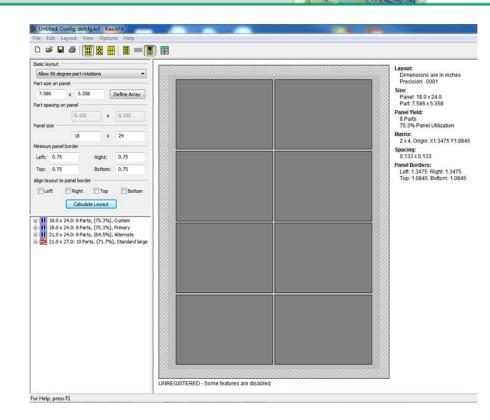

# Fabrication Panel Design

- Panel Design is a Primary Cost Driver for PCB

- % Utilization of the Master Panel will typically be the main cost

- Pushing ownership to the fabricator or manufacturer will have it's PROS and CONS.

- It is important that both the fabricator and the manufacturer needs are taken into consideration and collaborative ownership of panel design should be carefully considered.

PCB Cost Project A

### **Scope of the Project**

Optimized panel design to meet automated equipment requirements based on EAU increased the master panel utilization from 52% to 72% yielding 20% more panels than the existing design and providing high throughput and lower cost per unit.

### **Value Engineering Services Implemented**

Cost Savings

PCB Panel Design

• \$20K

### **PCB Material Specification**

**Project B**

### **Scope of the Project**

Relax Tg constraints for 10 layer board and realize savings by switch from S1000-2 (Tg 170) to IT158 (Tg 150) with existing supplier

### **Value Engineering Services Implemented**

**Cost Savings**

Design for Fabrication

\$34K

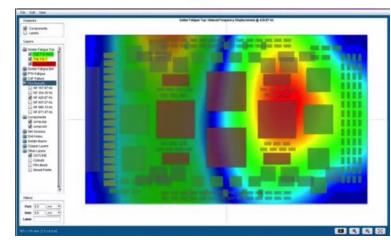

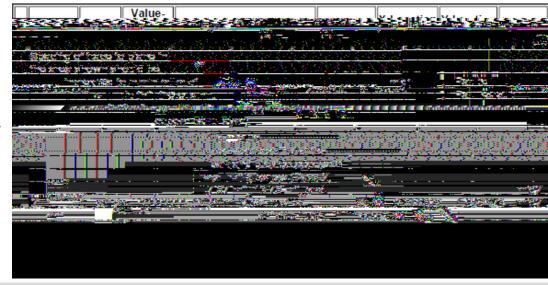

# Design for Testability (DFT)

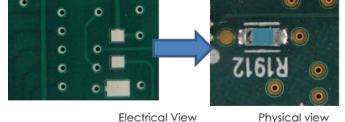

- Post Routing release enables a physical view of the PCB and actual test points, size and location.

- Physically assigned probe access are analyzed by assigning test point and generating nail rules, keep outs to the design

- Component level coverage for Placement, Functionality, Solderability and Value are provided.

|       | F   | PART | INF | 0   |       |     |     |     |     |    | NT<br>5D | X) |    |   |    |     |    | .ITY<br>5DX |     |     |     | ALI<br>IC |     |      |     | so  | LDI | ERA | BIL | LITY |      |     |    |     |      | ECK<br>DX) | % COVE  | RAGE  |

|-------|-----|------|-----|-----|-------|-----|-----|-----|-----|----|----------|----|----|---|----|-----|----|-------------|-----|-----|-----|-----------|-----|------|-----|-----|-----|-----|-----|------|------|-----|----|-----|------|------------|---------|-------|

| REFID | PLA | CED  | TYI | PEP | DLARI | TY. | AOI | :IC | T:5 | DX | FIN      | AL | AC | H | СТ | 5D) | ΧF | INA         | LΙΑ | OI: | ICT | :5L       | X   | FINA | L A | 10/ | ICT | :5D | XF  | INA  | _:AC | ) i | СТ | 5D) | K FI | NAL        | OVERALL | FINAL |

| C1    |     | 1    | С   |     | 1     |     | 1   | 0   | 1   | 1  | 1        |    | 1  | Т | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   | 7   | 1    | 1    | Ŧ   | 0  | 1   | Т    | 1          | 90%     | 90%   |

| C10   |     | 1    | С   |     | 1     |     | 1   | 0   |     | 1  | 1        |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   |     | 1    | 1    |     | 0  | 1   |      | 1          | 90%     | 90%   |

| C100  |     | 1    | С   |     | 1     |     | 1   | : 0 |     | 1  | 1        |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   |     | 1    | 1    |     | 0  | 1   |      | 1          | 90%     | 90%   |

| C1000 |     | 1    | : C |     | 1     |     | 1   | : 0 | -   | 1  | : 1      |    | 1  | т | 0  | 1   | -  | 0           |     | 1   | 0   | : (       | ) : | 0    |     | 0   | 0   | 1   | - 1 | 1    | : 1  | -   | 0  | 1   |      | 1          | 90%     | 90%   |

| C1001 |     | 1    | С   |     | 1     |     | 1   | 0   | T   | 1  | 1        |    | 1  | Т | 0  | 1   |    | 0           |     | 1   | 0   | . (       | )   | 0    |     | 0   | 0   | 1   | T   | 1    | 1    | T   | 0  | 1   | Т    | 1          | 90%     | 90%   |

| C1002 |     | 1    | : C |     | 1     |     | 1   | 0   | -   | 1  | 1        |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   | - 1 | 1    | 1    | Т   | 0  | 1   |      | 1          | 90%     | 90%   |

| C1003 |     | 1    | C   |     | 1     |     | 1   | : 0 | -   | 1  | 1        |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   | - 1 | 1    | 1    | - 1 | 0  | 1   |      | 1          | 90%     | 90%   |

| C1004 |     | 1    | С   |     | 1     |     | 1   | 0   | 1   | 1  | 1        |    | 1  | Т | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   | Ŧ   | 1    | 1    | Ŧ   | 0  | 1   | Т    | 1          | 90%     | 90%   |

| C1005 |     | 1    | С   |     | 1     |     | 1   | 0   | T   | 1  | 1        |    | 1  | Т | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   | T   | 1    | 1    | Т   | 0  | 1   | Т    | 1          | 90%     | 90%   |

| C1006 |     | 1    | C   |     | 1     |     | 1   | : 0 |     | 1  | 1        |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | . (       | )   | 0    |     | 0   | 0   | 1   |     | 1    | 1    |     | 0  | 1   |      | 1          | 90%     | 90%   |

| C1007 |     | 1    | : C |     | 1     |     | 1   | 0   | -   | 1  | 1        |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   | - 1 | 1    | : 1  | - 1 | 0  | 1   |      | 1          | 90%     | 90%   |

| C1008 |     | 1    | С   |     | 1     |     | 1   | 0   |     | 1  | 1        |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | . (       | )   | 0    |     | 0   | 0   | 1   |     | 1    | 1    |     | 0  | 1   |      | 1          | 90%     | 90%   |

| C1009 |     | 1    | С   |     | 1     |     | 1   | 0   | 1   | 1  | 1        |    | 1  | Т | 0  | 1   |    | 0           |     | 1   | 0   | . (       | )   | 0    |     | 0   | 0   | 1   | 1   | 1    | 1    | Т   | 0  | 1   | Т    | 1          | 90%     | 90%   |

| C101  |     | 1    | С   |     | 1     | - 1 | 1   | 1   | -   | 1  | 1        |    | 1  |   | 1  | 1   |    | 1           | -   | 1   | 1   | : (       | ) : | 1    |     | 0   | 0   | 1   |     | 1    | . 1  |     | 0  | 1   |      | 1          | 130%    | 99%   |

| C1010 |     | 1    | : C |     | 1     |     | 1   | : 0 | -   | 1  | 1        |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | : (       | ) : | 0    |     | 0   | 0   | 1   |     | 1    | 1    |     | 0  | 1   |      | 1          | 90%     | 90%   |

| C1011 |     | 1    | С   |     | 1     |     | 1   | 0   | 7   | 1  | 1        |    | 1  | Т | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   | 7   | 1    | 1    | 7   | 0  | 1   |      | 1          | 90%     | 90%   |

| C1012 |     | 1    | С   |     | 1     |     | 1   | 0   |     | 1  | 1        |    | 1  | Т | 0  | 1   |    | 0           |     | 1   | 0   | ; (       | )   | 0    |     | 0   | 0   | 1   | 1   | 1    | 1    | 1   | 0  | 1   | 1    | 1          | 90%     | 90%   |

| C1013 |     | 1    | C   |     | 1     |     | 1   | 0   | 1   | 1  | . 1      |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | : (       | )   | 0    |     | 0   | 0   | 1   |     | 1    | : 1  | Т   | 0  | 1   |      | 1          | 90%     | 90%   |

| C1014 |     | 1    | С   |     | 1     |     | 1   | : 0 |     | 1  | 1        |    | 1  |   | 0  | 1   |    | 0           |     | 1   | 0   | (         | )   | 0    |     | 0   | 0   | 1   |     | 1    | 1    |     | 0  | 1   |      | 1          | 90%     | 90%   |

| C1015 |     | 1    | С   |     | 1     |     | 1   | 0   |     | 1  | 1        |    | 1  | Т | 0  | 1   |    | 0           |     | 1   | 0   | (         | )   | 0    |     | 0   | 0   | 1   |     | 1    | 1    | Т   | 0  | 1   | Т    | 1          | 90%     | 90%   |

0 = Not Tested

C = Capacitor

L = Inductors

J = Jumper orD = Diode

U = Integrated

T = Transform

X = Crystal or RN = Resistor

Fault coverage

CIM

## Electrical Testing (Value/Polarity)

- Typically involve opens, shorts, impedance and net verification. Powered tests are available to provide some additional coverage options.

- Strategies include Manufacturing Defect Analyzer (MDA) Flying Probe,

## Structural Testing (Placement/Polarity)

- Typically detects presence, absence, orientation/polarity and solder joint integrity.

- Strategies include Visual Inspection, X-Ray (2D or 3D) and Automated Optical Inspection (AOI)

## Functional Testing (Functionality)

- Typically involve expected input and output simulation of the end application and exercising of core circuitry to validate final functionality

- Strategies include In-Circuit Test (ICT) and Functional Test (FT)

## Reliability Testing (Validation)

- Typically involve cycling power / temperature over a statistically determined period to identify pre-mature electrical or structural failure that may effect long term reliability

- Strategies include Run-in, Burn-in and Environmental Stress Screening (ESS)

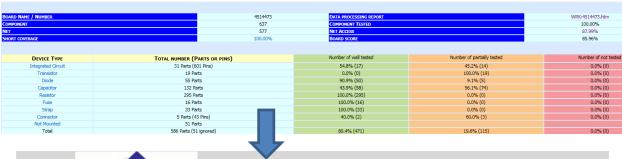

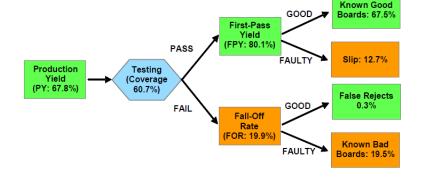

# Test Strategy Analysis

A = AOI

X = XRAY W = Flying Probe I = ICT F = Funct Test

Quality

Test Strategy Analysis provides an overview of current coverage proposed test strategy, expected yield assumptions, coverage gaps and expected RMA.

- Recommend Test Strategy for optimum coverage and efficiency

- Generate Return on Investment based on FAU and lifecycle to design/optimize Test Plan.

### **TEST REPORT FOR ICT, AOI**

### TEST STRATEGY ROI SUMMARY

Product p/n Quote:

|                 |      | Expected<br>Final Yield |        |         |         | Expected<br>ICT Yield | Expected<br>Functional<br>Yield | Escapes<br>(Coverage<br>Gaps) | RMA RMA | NRE          | ROI | (yrs)  | Cost of<br>Quality | Savings |

|-----------------|------|-------------------------|--------|---------|---------|-----------------------|---------------------------------|-------------------------------|---------|--------------|-----|--------|--------------------|---------|

| oted Process -> | v    | 99.91%                  |        |         | -       |                       |                                 | 0.03%                         | 0.12%   | \$0.00       |     | 0.00   | \$120.56           | \$0.0   |

|                 | v    | 99.91%                  |        |         |         |                       |                                 | 0.03%                         | 0.12%   | \$ -         |     | 0.00   | \$120.56 \$        |         |

|                 | A    | 99.94%                  | 99.94% |         |         |                       | 4 9                             | 0.00%                         | 0.07%   | \$ 300.00    | S . | 5.86   | \$69.34 \$         | 51.22   |

|                 | x    | 99.92%                  |        | 99.95%  |         |                       |                                 | 0.00%                         | 0.08%   | \$ 750.00    |     | 20.35  | \$83.70 \$         | 36.86   |

|                 | w    | 99.95%                  | 0      | -       | 99.92%  |                       |                                 | 0.00%                         | 0.05%   | \$ 1,200.00  |     | 17.04  | \$50.14 \$         | 70.42   |

|                 | 1    | 99.99%                  |        |         |         | 99.88%                |                                 | 0.00%                         | 0.01%   | \$ 14,300.00 |     | 134.04 | \$13.88 \$         | 106.68  |

|                 | F    | 99.99%                  |        |         |         |                       | 99.88%                          | 0.00%                         | 0.01%   | \$ 9,000.00  |     | 82.09  | \$10.92 \$         | 109.64  |

|                 | AX   | 99.94%                  | 99.93% | 100.00% | 1       |                       |                                 | 0.00%                         | 0.06%   | \$ 1,050.00  |     | 19.86  | \$67.69 \$         | 52.87   |

|                 | AW   | 99.97%                  | 99.90% |         | 100.00% |                       |                                 | 0.00%                         | 0.03%   | \$ 1,500.00  |     | 17.82  | \$36.40 \$         | 84.16   |

|                 | AI   | 99.99%                  | 99.88% |         |         | 100.00%               |                                 | 0.00%                         | 0.01%   | \$ 14,600.00 |     | 133.51 | \$11.20 \$         | 109.36  |

|                 | AF   | 100.00%                 | 99.88% |         | l l     |                       | 100.00%                         | 0.00%                         | 0.00%   | \$ 9,300.00  |     | 82.84  | \$8.29 \$          | 112.2   |

|                 | xw   | 99.97%                  |        | 99.90%  | 100.00% |                       |                                 | 0.00%                         | 0.03%   | \$ 1,950.00  |     | 23.30  | \$36.86 \$         | 83.70   |

|                 | X I  | 99.99%                  | - 3    | 99.88%  |         | 100.00%               | Y                               | 0.00%                         | 0.01%   | \$ 15,050.00 | 1   | 137.33 | \$10.97 \$         | 109.5   |

|                 | XF   | 99.99%                  |        | 99.88%  |         |                       | 100.00%                         | 0.00%                         | 0.01%   | \$ 9,750.00  |     | 88.15  | \$9.95 \$          | 110.6   |

|                 | I F  | 100.00%                 |        |         |         | 99.88%                | 100.00%                         | 0.00%                         | 0.01%   | \$ 23,300.00 | 1 3 | 209.97 | \$9.59 \$          | 110.9   |

|                 | WF   | 100.00%                 |        | - 2     | 99.88%  |                       | 100.00%                         | 0.00%                         | 0.01%   | \$ 10,200.00 |     | 92.50  | \$10.29 \$         | 110.2   |

|                 | AXW  | 99.97%                  | 99.90% | 100.00% | 100.00% |                       |                                 | 0.00%                         | 0.03%   | \$ 2,250.00  |     | 25.82  | \$33.43 \$         | 87.13   |

|                 | AXI  | 99.99%                  | 99.88% | 100.00% |         | 100.00%               | ŧ ï                             | 0.00%                         | 0.01%   | \$ 15,350.00 |     | 139.19 | \$10.28 \$         | 110.2   |

|                 | AXF  | 100.00%                 | 99.88% | 100.00% |         |                       | 100.00%                         | 0.00%                         | 0.00%   | \$ 10,050.00 |     | 89.28  | \$8.00 \$          | 112.5   |

|                 | AWF  | 100.00%                 | 99.87% |         | 100.00% |                       | 100.00%                         | 0.00%                         |         |              |     | 91.39  | \$5.67 \$          | 114.89  |

|                 | AIF  | 100.00%                 | 99.87% |         |         | 100.00%               | 100.00%                         | 0.00%                         |         | \$ 23,600.00 |     | 204.27 | \$5.03 \$          | 115.5   |

|                 | XIF  | 100.00%                 |        | 99.88%  |         | 100.00%               | 100.00%                         | 0.00%                         |         |              |     | 211.62 | \$6.92 \$          |         |

|                 | XWF  | 100.00%                 |        | 99.88%  | 100.00% |                       | 100.00%                         | 0.00%                         | 0.00%   | \$ 10,950.00 |     | 96.84  | \$7.49 \$          |         |

|                 | AXIF | 100.00%                 | 99.87% | 100.00% |         | 100.00%               | 100.00%                         | 0.00%                         | 0.00%   | \$ 24,350.00 |     | 210.08 | \$4.65 \$          | 115.91  |

|                 | AXWF | 100.00%                 | 99.88% | 100.00% | 100.00% |                       | 100.00%                         | 0.00%                         | 0.00%   | \$ 11,250.00 |     | 98.06  | \$5.83 \$          | 114.73  |

1. A key parameter for quantifying costs is the expense involved in processing field returns. This figure has been estimated at \$17.09 per card but should ideally should be set by the customer

### **Test Strategy Recommendation**

**Project A**

### **Scope of the Project**

Review existing test strategy and coverage to determine optimal test strategy to provide highest first pass yield, lowest coverage gaps, RMA and overall cost of quality.

### **Value Engineering Services Implemented**

### **Potential Savings**

- Design for Test

— Recommend AOI and ICT (FCT only required if full analog frequency testing required) over existing AOI and 5DX testing (no electrical). Reduce coverage gaps from 0.24% to 0.04% and expected RMA from 11.38% to 3.94%. ROI 0.20 years.

- \$89K \$18K = \$61K

ICT Development – Quote includes all aspects of ICT development, including future maintenance and production support.

Architecture

High Level Design Physical Design

Prototype

**Validation**

NPI

Volume

- Quick Turn Prototyping

- Distribution Procurement

- Local Suppliers (may or may not be same suppliers as production)

- Usually structural and/or fixtureless electrical testing

- Proof of Concept or early Alpha/Beta builds

- Initial FMEA and Control Plan Development

## Who should be engaged?

- Critical Component Suppliers

- Manufacturer

- Test Engineering

- Quality

## **DfX Review**

- Design for Manufacturability (DFM)

- Equipment Requirements

- Tooling Considerations

- Process Considerations

- Labor Requirements

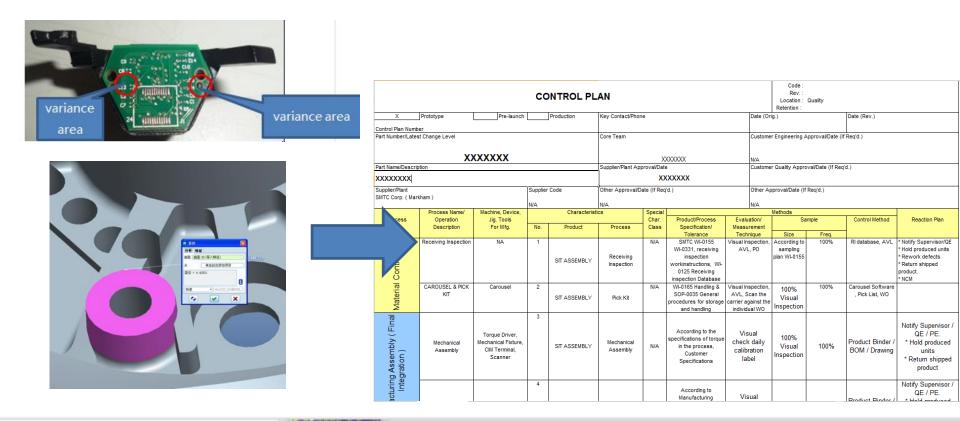

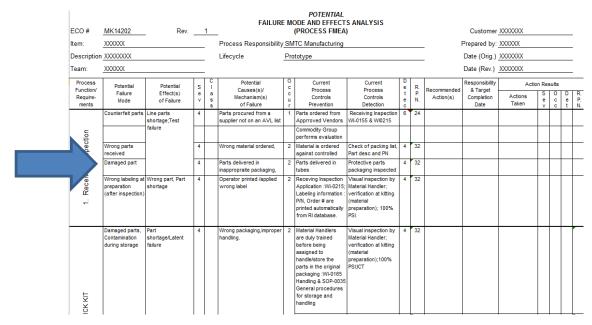

# Design for Manufacturing (DFM)

DFM incorporate supplier specific equipment requirements, specific manufacturer process requirements are applied to develop the process and ultimately the Control Plan to effectively address the pFMEA.

Architecture

High Level Design Physical Design

Prototype

Validation

NPI

Volume

- Design Verification Testing (DVT)

- Highly Accelerated Life Test (HALT)

- Highly Accelerated Stress Screen (HASS)

## Who should be engaged?

- Reliability Engineering

- Test Engineering

- Quality

## **DfX Review**

- Design for Reliability (DFR)

- HASS/HALT Failure Mode Inputs

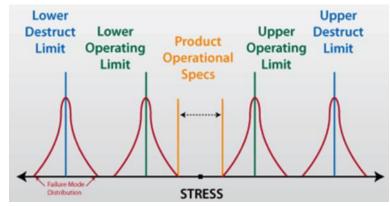

# Design for Reliability (DFR)

- Validation is intended to exercise the design within and outside their indeed specifications with the objective to test the limits of the design.

- Test Plans may include

- Design Verification Test

- Utilizes relatively low stresses and requires many cycles

- Design Vibration, Drop and Impact

- Design Highly Accelerated Life Test (HALT)

- Purpose to determine the operating and destructive limits of a design.

- Verify designs, component selections and manufacturing processes

- Design Highly Accelerated Stress Screen (HASS)

- Test methods specifically designed on finding defects in products

A traditional DFR "test-in reliability" approach which is valuable to identify "weak links" provides closed loop validation in conjunction with DfX methodology to further improve value.

Architecture High Level Physical Prototype Validation NPI

VOlume

- Final Design Release

- Volume Production Supplier Awards

- Critical Component and Control Plan in Place

- Introduction of Production Tooling/Process

- Master Validation Process Plan

- IQ, OQ, PQ Development

## Who should be engaged?

- Critical Component Suppliers

- Manufacturers/ Procurement

- Test Engineering

- Quality

## **DfX Review**

- Design for Manufacturability (DFM)

- First Article Reports

- Process Development (pFMEA)

- Yield and Detractor Analysis

- Problematic Design Improvements

- Design for Testability (DFT)

- Coverage Gap Strategy

## pFMEA - Process Failure Modes and Effects Analysis

Early Supplier involvement and detailed DFX inputs provide invaluable insight when developing the FMEA and should be mandated across all suppliers where practical.

### Areas reviewed include

- First Article Routing and Cycle Time

- Automation Panel Design, Supply Compatibility

- Tooling Stencils, Pallets, Other

- Process SMD, Reflow, Wave, Mechanical

- Misc. Process Conformal Coating, Cabling, System Integration

- Program Parts

- AOI/5DX Testing

- FP/ICT/FT Testing

- Hi-Pot/ESS Testing

- Misc. Testing Buss out, continuity

- Quality First Pass Yield, Top 5 detractors

- First Article Sign Off

Architecture

High Level Design Physical Design

Prototype

**Validation**

NPI

Volume

- Full Production Ramp/ Sustaining

- Stable Process and Test

- Duplication of existing Process/ Test Equipment (Capacity/ Throughput)

- Continuous Improvement

- Value Engineering

## Who should be engaged?

- Critical Component Suppliers

- Manufacturers

- Test Engineering

- Process Engineering

- Quality Engineering

## **DfX Opportunities**

- Design for Supply Chain (DFSC)

- EOL and PCN Management

- Cost Reduction

- Design for Testability (DFT)

- Test Improvements/ Reductions

- Design for Manufacturing (DFM)

- Process Improvements

# Early Supplier Involvement Benefits

- Early design interface and collaboration among designers, buyers, and suppliers throughout the product development cycle significant improves the ability to impact to the design.

- Identifying risks early enable customers to better manage their design

- Resulting overall lower project costs and higher <u>VALUE</u> <u>Products</u>

## **SMTC** Corporation

## **THANK YOU**

# **Engineering Work Plan**

## **DFX Engagement Case Study**

## Examples

- Design for Supply Chain (DFSC)

- Perform BOM and Lifecycle Analysis to identify EOL and discontinued early in the procurement cycle.

- Supported last time buy and provided FFF alternates to support design

- Performed AML Expansion to provide cost savings and supply chain flexibility

- Performed Stack up Tolerance and Interference Analysis to identify manufacturing and assembly issues.

- Performed Valor virtual part and DFM analysis of all printed circuit boards to identify assembly and design related issues.

- Incorporated early supplier involvement and DFM with key Metal, PCB and Plastic Suppliers

- Established manufacturing tolerances and capabilities into tolerance and stack up to provide critical dimensions to ensure function of final unit.

### Design for Testability

- Performed Board and System level schematic review

- Utilizing Test Expert performed Nodal access and Coverage Reporting

- Provided Test Strategy Analysis and Functional Recommendation

- Combined Solidworks models and perform Analysis

- Re-layout flex cable to optimize via positions and decrease connector footprint

- Re-layout sensor board to move traces and address shorting issues

- Develop custom automated lens focusing and system level test fixture.